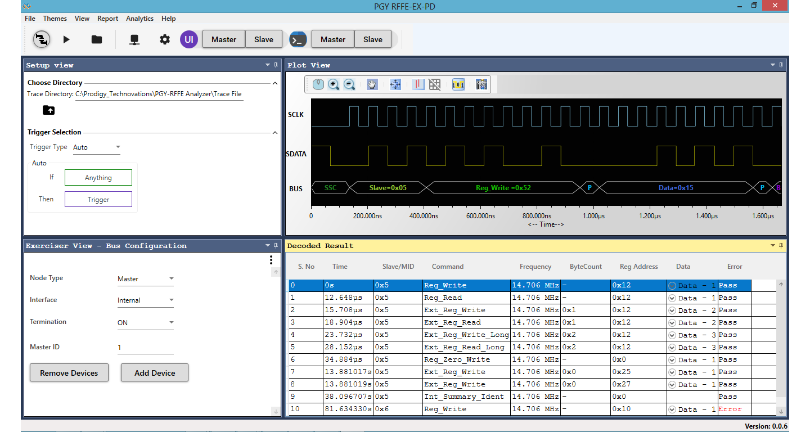

序列的每個步驟被稱為一個序列步驟。每個序列步驟由兩部分組成:條件和操作。條件是指布爾邏輯表達式,例如“IfADDR=1000”或“IfthereisarisingedgeonSIG1”。操作是指符合條件時邏輯分析儀應當執行的內容。操作的示例包括觸發邏輯分析儀、轉至另一序列步驟以及啟動定時器。這類似于編程中的If/Then語句。觸發序列中的每個步驟都被指定一個數字。執行的個序列步驟總是序列步驟1,但由于“轉到”操作,剩余的序列步驟可以以任意順序執行。執行一個序列步驟且布爾邏輯表達式均為假時,邏輯分析儀將采集下一樣本并再次執行同一序列步驟于“KeepacquiringmoresamplesuntilDATA=7000,thentrigger”。如果符合一個序列步驟中的布爾邏輯表達式,那么在執行下一序列步驟之前總是采集另一樣本。換句話說,如果一個樣本符合序列步驟1的條件,在執行序列步驟2前將采集另一樣本。這意味著一個單獨的樣本不可能符合多個序列步驟的條中的條件二者之間采集了新的樣本,因此邏輯分析儀不會在采集樣本#1時觸發。可將此觸發序列看作是“FindADDR=1000followedbyDATA=2000andthentrigger”。觸發序列中的多序列步驟暗示了“后接”。邏輯分析儀觸發后,將不會再次觸發。換句話說。USB PD,3.1, 3.0,2.0協議分析儀/訓練器找歐奧!成都RFFE分析儀廠家

當設置較難的觸發時,可將問題分解為若干較小的部分,然后逐個解決。邏輯分析儀探頭邏輯分析儀的探頭是邏輯分析儀非常重要的一部分。因為邏輯分析儀主要用于在線測量,探頭提供了與被測件的電氣和機械連接,當我們選擇探頭時,這兩個方面都是主要考慮因素。如下圖所示,探頭被動的觀察目標信號,目標信號的一小部分進入探頭,通過互連線纜傳遞到邏輯分析儀模塊,邏輯分析儀模塊里面的放器把這一小部分信號放,還原原始波形。探頭的電氣性能主要考慮2個方面,這與示波器探頭的考慮因素是一致的。1)不要干擾目標信號(探頭的信號完整性)2)模塊內能夠較精確的復現被測信號(探頭的信號保真度)圖22邏輯分析儀的探測探頭的結構細分下來也是比較復雜的。探頭與被測傳輸線接觸的小互連部分,可以使用PCB走線的方式,也可以使用導線,連接器或彈簧片,要根據實際情況選擇。探頭的前端包含電阻,有的是分立的SMT電阻,有的是分立電阻,一般阻值都在20k歐姆左右。探頭前端到模塊有長的電纜,已達到便于連接遠近目標的方便性,這些電纜可使用同軸方式或使用雙絞線方式,但都要保證足夠的帶寬。邏輯分析儀模塊需要對電纜的阻抗進行匹配,防止傳遞過來的信號反射回去。江門邏輯分析儀價格歐奧協議分析儀是眾多客戶明智的選擇!

內存深度設置為總采集內存的1/2。所有盒對都可用于采集數據。如果選擇整個內存,則要用于時間標簽存儲的默認Pod是左邊的盒對,但未分配總線或信號的任何Pod都是可以使用的。跳變定時模式,時間標簽存儲需要1個Pod或1/2的采集內存:跳變時序采樣模式也需要時間標簽存儲。當選擇小采樣周期時,必須將一個Pod對保留用于時間標簽存儲。在這種情況下,不能使用1/2(或更少)的模塊采集內存來替代該Pod。對于其他采樣周期,內存深度和通道數的權衡與狀態采樣模式下的相同。也就是說,要使用1/2以上的模塊采集內存,必須將一個Pod保留用于時間標簽存儲。要使用所有Pod,內存使用量不能超過模塊采集內存的1/2。一般來說,可用定時器數與那些不屬于為時間標簽存儲而保留的Pod數相同。狀態模式采樣位置、眼定位和眼圖掃描同步采樣(狀態模式)邏輯分析儀與觸發時鐘沿的觸發相似,因為它們都需要輸入邏輯信號才可以在時鐘事件前(建立時間)和時鐘事件后(保持時間)的一段時間內保持穩定,以便正確解釋邏輯電平。組合建立和保持時間被稱為建立/保持窗口。被測設備(由于其本身的建立/保持要求)可指定數據在某段時間內在總線上有效。這被稱為數據有效窗口。一般情況下。

將內存深度設置為值的一半(或更小)將返回Pod。在狀態采樣模式中,在選擇了高速狀態模式采樣選項的情況下,會將一個Pod對保留用于時間標簽存儲。在定時采樣模式中,在選擇了跳變/存儲限定定時模式采樣選項的情況下:選擇了小采樣周期時,會將一個Pod對保留用于時間標簽存儲。選擇了除小采樣周期之外的采樣周期時,選擇采集內存深度需要將一個Pod對保留用于時間標簽存儲。在這種情況下,將內存深度設置為值的一半(或更小)將返回Pod。該模塊是已分離的邏輯分析儀的一部分。在這種情況下,Pod位于分離分析儀的另一半模塊中。狀態模式和跳變定時模式下通道數、內存深度和觸發之間的相互影響:狀態采樣模式時,時間標簽存儲需要1個Pod或1/2的采集內存。在操作界面應用程序中,所有模塊都與時間相關;不能關閉timetagstorage(時間標簽存儲)(雖然以前的Agilent邏輯分析系統可以)。要使用1/2以上的模塊采集內存,必須將一個Pod保留用于時間標簽存儲。要使用所有Pod,內存使用量不能超過模塊采集內存的1/2。一般來說,可用定時器數與那些不屬于為時間標簽存儲而保留的Pod數相同。默認設置:時間標簽存儲始終處于開啟狀態(并且不能將其關閉)。PMBus協議分析儀/訓練器找歐奧!

序列步驟存儲總會覆蓋默認存儲,但只針對序列步驟存儲中特別指定的條件。處理默認存儲和序列步驟存儲之間的時一定要謹慎。雖然設置邏輯分析儀很困難,但觸發函數可以降低此過程的難度。觸發函數是可以組合起來設置觸發的常用構建塊。由于這些函數涵蓋了多數普通觸發,因此通過選擇適當的函數并將其填充到數據中即可設置觸發。下圖顯示了邏輯分析儀觸發用戶界面。請注意,觸發函數位于屏幕左側的一個醒目位置。圖21使用觸發函數通常,設置復雜觸發的難題是對問題進行分解。換句話說,就是如何將復雜觸發映射到序列步驟、分支和布爾邏輯表達式。將問題分解為不同時發生的事件。這些事件對應于序列步驟。掃描觸發函數列表,嘗試找出一些與步驟1中確定的事件相匹配的函數。將所有剩余事件分解為布爾邏輯表達式及其相應操作。各個布爾邏輯表達式/操作對分別對應于序列步驟中的一個單獨分支。請記住,可能存在只用于為序列步驟處理存儲限定的“存儲”分支。設置邏輯分析儀觸發與編寫軟件相徑庭。如果使用預定義的觸發函數和較早編寫的文檔完善的觸發來完成其他工作,就可降低設置邏輯分析儀觸發的難度。在沒有其他可用的資源時,才需要編寫自己的觸發設置。后。LLI協議分析儀/訓練器找歐奧!肇慶協議分析儀費用

HSIC協議分析儀/訓練器找歐奧!成都RFFE分析儀廠家

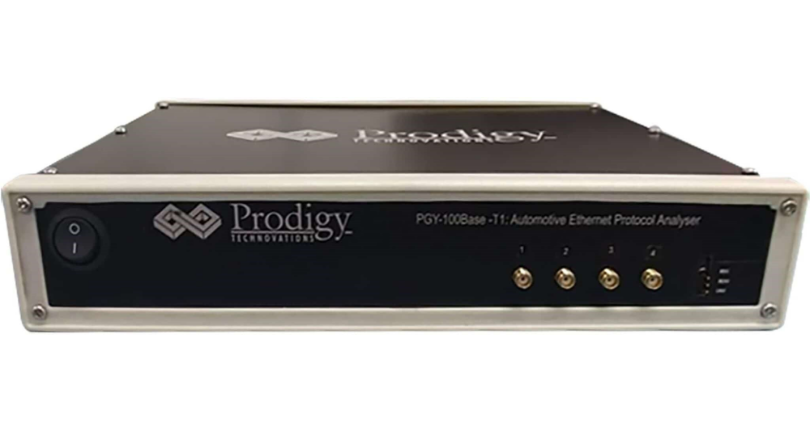

歐奧電子是Prodigy在中國區的官方授權合作伙伴,ProdigyMPHY,UniPro,UFS總線協議分析儀測試解決方案不會收到EAR進出口方面的管制。同時還有代理其他總類的協議分析儀,包括嵌入式設備用的SDIO協議分析儀,QSPI協議分析儀及訓練器,I3C協議分析儀及訓練器,RFFE協議分析儀及訓練器等等。我司還有代理SPMI協議分析儀及訓練器,車載以太網分析儀,以及各種相關的基于示波器的解碼軟件和SI測試軟件。同時,歐奧電子也有提供高難度焊接,以及高速信號,如UFS,DDR3/DDR4,USBtypeC等高速協議抓取和分析的服務。DampedResistorProbing),電阻匹配探測(ResistiveDividerProbing)。短線探測會增加電容負載。舉例:探頭電容負載是,連接短線是50歐姆微帶線。C=3pF/in),長度1英寸。則整個探頭的電容負載是,這個短線是電容負載的主要部分。被測系統可容忍的負載電容是多少呢?需要參考被測電路的系統上升時間,一般規則:短線的電氣長度<>PCB傳輸延遲:150ps/in系統上升時間:500ps則電氣長度:則短線長度:(100ps)/(150ps/in)=。如果沒法減小短線長度,可以試著用阻尼電阻探測的方式。阻尼電阻有2個作用:隔離來自短線的電容,消減來自短線的反射。成都RFFE分析儀廠家